TQ H503A

Overview

The Embedsky TQ-H503A board is an extremely low cost and bare-bones development board featuring an ARM® Cortex®-M33 core-based STM32H503CBT6 microcontroller, see STM32H503CB website [1]. This is the 48-pin variant of the STM32H503x series, see STM32H503x reference manual [2]. Here are some highlights of the TQ-H503A board:

STM32H503CB microcontroller with 128 Kbytes of Flash memory and 32 Kbytes of SRAM in LQFP48 package

One user LED

32.768 kHz crystal oscillator

8 MHz HSE crystal oscillator

Hardware

The STM32H503CB belongs to the high-performance microcontroller family (STM32H5 series) based on the high-performance Arm® Cortex®-M33 32-bit RISC core. They operate at frequency of up to 250 MHz.

Core: Arm® Cortex®-M33 CPU with FPU, MPU, 375 DMIPS (Dhrystone 2.1), and DSP instructions

ART Accelerator

Memories

128 Kbytes of embedded flash memory with ECC, two banks of read-while-write

2-Kbyte OTP (one-time programmable)

32-Kbyte SRAM with ECC

2 Kbytes of backup SRAM (available in the lowest power modes)

Clock management

Internal oscillators: 64 MHz HSI, 48 MHz HSI48, 4 MHz CSI, 32 kHz LSI

Two PLLs for system clock, USB, audio, and ADC

External oscillators: 4 to 50 MHz HSE, 32.768 kHz LSE

Embedded regulator (LDO)

35 fast I/Os (most 5 V tolerant)

Analog peripherals

1x 12-bit ADC with up to 2.5 MSPS

1x 12-bit dual-channel DAC

1x ultra-low-power comparator

1x operational amplifier (7 MHz bandwidth)

1x Digital temperature sensor

11 timers - 4x 16-bit - 1x 32-bit - 2x 16-bit low-power 16-bit timers (available in Stop mode) - 2x watchdogs - 1x SysTick timer - RTC with HW calendar, alarms and calibration

16x communication interfaces

2x I2Cs FM + interfaces (SMBus/PMBus®)

2x I3Cs shared with I2C

3x USARTs (ISO7816 interface, LIN, IrDA, modem control)

1x LPUART

3x SPIs including three muxed with full-duplex I2S

3x additional SPI from 3x USART when configured in synchronous mode

1x FDCAN

1x USB 2.0 full-speed host and device

Two DMA controllers to offload the CPU

Security

HASH (SHA-1, SHA-2), HMAC

True random generator

96-bit unique ID

Active tamper

Development support: serial wire debug (SWD) and JTAG interfaces

Supported Features

The tq_h503a board supports the hardware features listed below.

- on-chip / on-board

- Feature integrated in the SoC / present on the board.

- 2 / 2

-

Number of instances that are enabled / disabled.

Click on the label to see the first instance of this feature in the board/SoC DTS files. -

vnd,foo -

Compatible string for the Devicetree binding matching the feature.

Click on the link to view the binding documentation.

tq_h503a/stm32h503xx target

Type |

Location |

Description |

Compatible |

|---|---|---|---|

CPU |

on-chip |

ARM Cortex-M33 CPU1 |

|

ADC |

on-chip |

STM32 ADC1 |

|

CAN |

on-chip |

STM32 FDCAN CAN FD controller1 |

|

Clock control |

on-chip |

STM32H5 RCC (Reset and Clock controller)1 |

|

on-chip |

STM32 HSE Clock1 |

||

on-chip |

STM32 HSI Clock1 |

||

on-chip |

|||

on-chip |

STM32 LSE Clock1 |

||

on-chip |

|||

on-chip |

STM32 Microcontroller Clock Output (MCO)2 |

||

Counter |

on-chip |

STM32 counters5 |

|

CRC |

on-chip |

STM32 CRC calculation unit1 |

|

DAC |

on-chip |

STM32 family DAC1 |

|

DMA |

on-chip |

STM32U5 DMA controller2 |

|

Flash controller |

on-chip |

STM32 Family flash controller1 |

|

GPIO & Headers |

on-chip |

STM32 GPIO Controller5 |

|

I2C |

on-chip |

||

I2S |

on-chip |

STM32H7 I2S controller3 |

|

I3C |

on-chip |

STM32H5 I3C controller2 |

|

Interrupt controller |

on-chip |

ARMv8-M NVIC (Nested Vectored Interrupt Controller)1 |

|

on-chip |

STM32G0 External Interrupt Controller1 |

||

LED |

on-board |

Group of GPIO-controlled LEDs1 |

|

MMU / MPU |

on-chip |

ARMv8-M MPU (Memory Protection Unit)1 |

|

MTD |

on-chip |

STM32 flash memory1 |

|

NVMEM |

on-chip |

Fixed layout for Non-Volatile memory1 |

|

OTP memory |

on-chip |

||

PHY |

on-chip |

This binding is to be used by all the usb transceivers which are built-in with USB IP1 |

|

Pin control |

on-chip |

STM32 pin controller with High-Speed Low-Voltage (HSLV) support1 |

|

Power management |

on-chip |

STM32H5 I/O cell controller1 |

|

PWM |

on-chip |

STM32 PWM5 |

|

Reset controller |

on-chip |

STM32 Reset and Clock Control (RCC) Controller1 |

|

RNG |

on-chip |

STM32 Random Number Generator1 |

|

RTC |

on-chip |

STM32 RTC1 |

|

Sensors |

on-chip |

STM32 Digital Temperature Sensor1 |

|

on-chip |

STM32 family TEMP node for production calibrated sensors with two calibration temperatures1 |

||

on-chip |

STM32 VREF+1 |

||

on-chip |

STM32 VBAT1 |

||

Serial controller |

on-chip |

||

on-chip |

STM32 LPUART1 |

||

SMbus |

on-chip |

STM32 SMBus controller2 |

|

SPI |

on-chip |

||

Timer |

on-chip |

ARMv8-M System Tick1 |

|

on-chip |

STM32 low-power timer (LPTIM)2 |

||

on-chip |

STM32 timers5 |

||

USB |

on-chip |

STM32 USB controller1 |

|

Watchdog |

on-chip |

STM32 watchdog1 |

|

on-chip |

STM32 system window watchdog1 |

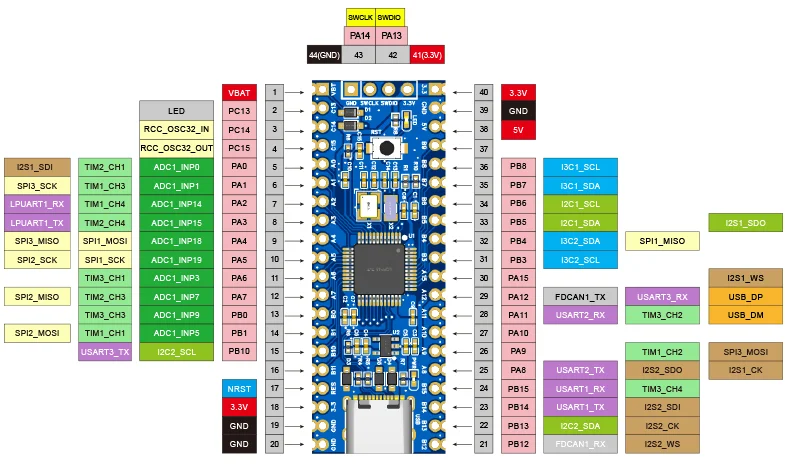

Pin Mapping

Available pins:

Default Zephyr Peripheral Mapping:

UART_1 TX/RX : PB14/PB15

USER_LED : PC13

I2C1 SCL/SDA : PB6/PB5

SPI1 SCK/MISO/MOSI : PA5/PB4/PA4 (Routed to footprint for external flash)

Clock Sources

The board has two external oscillators. The slow clock (LSE) runs at 32.768 kHz. The main clock (HSE) runs at 8 MHz.

By default, the system clock is sourced from the PLL, derived from HSE and set to 250 MHz.

Programming and Debugging

The tq_h503a board supports the runners and associated west commands listed below.

| flash | debug | attach | debugserver | rtt | |

|---|---|---|---|---|---|

| blackmagicprobe | ✅ | ✅ | ✅ | ||

| openocd | ✅ (default) | ✅ (default) | ✅ | ✅ | ✅ |

Applications for the tq_h503a board can be built and

flashed in the usual way (see Building an Application and

Run an Application for more details).

OpenOCD Support

Currently, upstream OpenOCD does not yet support STM32H5 devices. You can check the OpenOCD official Github mirror [3] for updates. To use OpenOCD with this board, clone the customized STMicroelectronics OpenOCD Github [4] repo and build it following the README. Once compiled, set the and OPENOCD_ROOT variables in boards/embedsky/tq_h503a/board.cmake to point to the OpenOCD binary and its scripts, before including the common openocd.board.cmake file:

set(OPENOCD_ROOT "<path_to_openocd_stm32_repo>")

set(OPENOCD "${OPENOCD_ROOT}/src/openocd" CACHE FILEPATH "" FORCE)

set(OPENOCD_DEFAULT_PATH ${OPENOCD_ROOT}/tcl)

Flashing

The board is configured for flashing using west openocd runner via ST-LINK:

$ west flash

Flashing an application to TQ-H503A

Attach an SWD debugger (ST-LINK) to the 3V3 (3.3V), GND, SCK, and DIO pins on the board.

Connect the debugger to your host via USB, then build and flash your application. For example, to flash the Hello World application.

Start a serial host program to connect to the debugger’s VCP:

$ minicom -D /dev/ttyACM0

Then build and flash the app:

# From the root of the zephyr repository

west build -b tq_h503a samples/hello_world

west flash

You should see the following message on the console:

Hello World! tq_h503a/stm32h503xx

Debugging

You can debug applications in the usual way. Here is an example for the Blinky application.

# From the root of the zephyr repository

west build -b tq_h503a samples/basic/blinky

west debug